john larkin

2024-09-06 22:50:28 UTC

I'm planning to use a Raspberry Pi RP2040 processor chip to configure

and then talk to an Efinix T20-FG256 FPGA.

Has anyone done this, or at least configured a T20 from a

microprocessor?

The RP2040 only has 30 GPIO pins, and many are dedicated to other

stuff, so we want to share a lot of things on one giant SPI bus,

including the FPGA config and then an SPI port on the FPGA to read and

write registers.

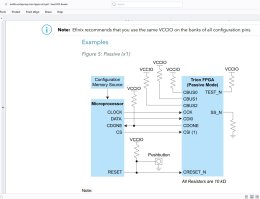

It looks like four of the T20 config pins need pullups. I wonder why

their guidelines show four separate resistors. Why not one resistor?

Why have resistors at all?

SS_N needs a pulldown. Why not ground it?

Loading Image...

It's always a moment to celebrate when a "config done" LED lights up.

I could easily get this wrong, so it would be great if I posted some

schematics and notes and someone could eyeball them for me.

and then talk to an Efinix T20-FG256 FPGA.

Has anyone done this, or at least configured a T20 from a

microprocessor?

The RP2040 only has 30 GPIO pins, and many are dedicated to other

stuff, so we want to share a lot of things on one giant SPI bus,

including the FPGA config and then an SPI port on the FPGA to read and

write registers.

It looks like four of the T20 config pins need pullups. I wonder why

their guidelines show four separate resistors. Why not one resistor?

Why have resistors at all?

SS_N needs a pulldown. Why not ground it?

Loading Image...

It's always a moment to celebrate when a "config done" LED lights up.

I could easily get this wrong, so it would be great if I posted some

schematics and notes and someone could eyeball them for me.